Verilog¶

Verilog is a hardware description language (HDL) used to model, simulate, and design digital circuits at various abstraction levels.

Verilog syntax defines the structure and rules for writing hardware models, while its data types describe signals, registers, and logic used in digital design.

Verilog supports various number representations, including binary, octal, decimal, and hexadecimal, with optional size and base specifications.

Verilog operators allow arithmetic, logical, and bit-wise operations on signals to define expressions and manipulate data in digital circuits.

In Verilog, modules are the basic building blocks of design, and hierarchy allows complex designs to be structured using nested modules.

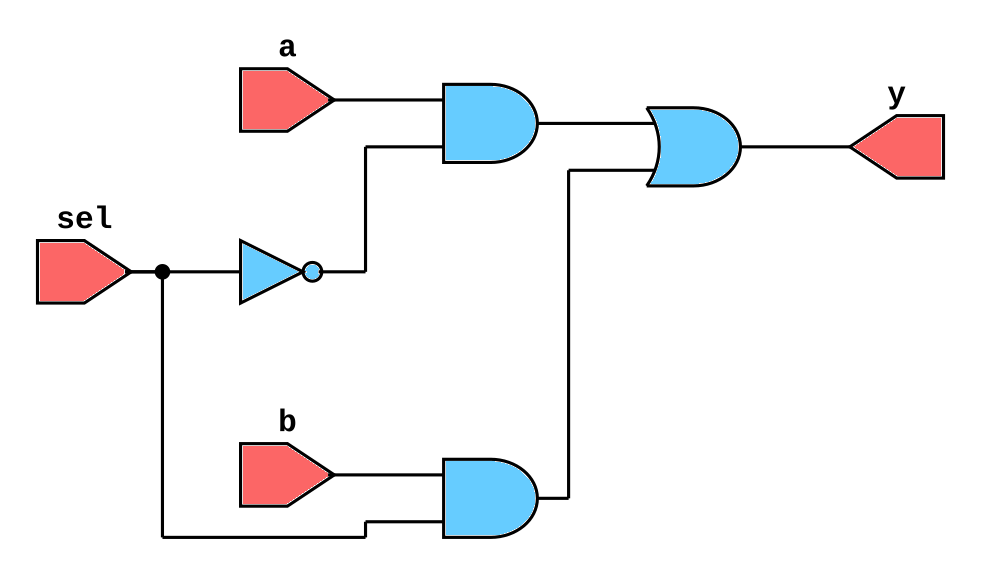

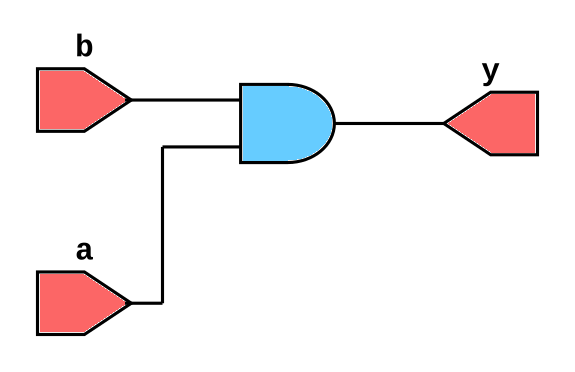

Gate-level modeling in Verilog represents digital circuits using logic gates such as AND, OR, NOT, NAND, and NOR to describe hardware at the structural level.

Data-flow modeling in Verilog describes digital circuits using continuous assignments that define how data moves between signals.

Behavioral modeling in Verilog describes a circuit’s functionality using high-level constructs like if, case, and loops, without focusing on hardware implementation details.

In Verilog, always blocks are used to describe behavior that executes repeatedly, while initial blocks run only once at the start of simulation.

Blocking and non-blocking assignments in Verilog control the execution order of statements, affecting how signals are updated during simulation.

In Verilog, combinational logic produces outputs based solely on current inputs, while sequential logic uses memory elements and clock signals to store and process data.

Simulation code in Verilog is used to verify design functionality, while synthesis code is written to generate actual hardware during FPGA or ASIC implementation.

Simulation code in Verilog is used to verify design functionality, while synthesis code is written to generate actual hardware during FPGA or ASIC implementation.

A Finite State Machine (FSM) in Verilog models a system that transitions between states based on inputs and clock signals.

Tasks and functions in Verilog are reusable blocks of code that help modularize designs, with tasks supporting delays and multiple outputs, unlike functions.

The generate statement in Verilog allows conditional or repetitive instantiation of modules and logic, enabling parameterized and scalable hardware designs.

The fork and join statements in Verilog allow parallel execution of multiple procedural blocks within simulations.

Compiler directives in Verilog are special instructions that control how the compiler processes the code, such as defining macros, including files, and setting timescales.